UVM:10.4.2 使用单独的参数类

本文共 436 字,大约阅读时间需要 1 分钟。

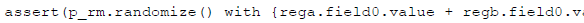

1.需要一种跨越寄存器的约束。要求2个field 的和大于100。只有上节第二种能实现:

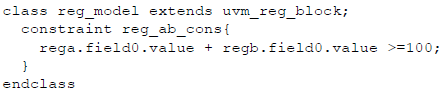

2.由于这个约束对所有测试都适用,因此希望写在寄存器模型的constraint 里:

3.这个寄存器模型使自己手工创建的,没问题。但在IC 中,寄存器模型都是由一些脚步命令自动创建的。在验证平台中,用到寄存器的地方有3个:

RTL

systemverilog

C语言

1)必须时刻保持这3 处的寄存器完全一致。有一处更新,其他两处必须更新。寄存器多,浪费时间。

2)IC 公司会将寄存器描述放在一个源文件中,使用脚本生成对应的3个模型。寄存器模型更新时,只更新源文件即可,省时省力,主流方式。

4.使用脚本创建时,在寄存器模型加入constraint 比较困难。很多寄存器模型的工具不支持约束。

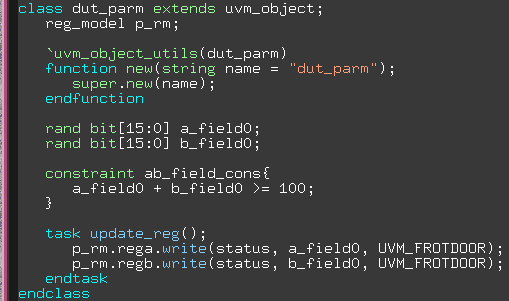

5.解决,建立一个dut_parm 类,在其中约束:

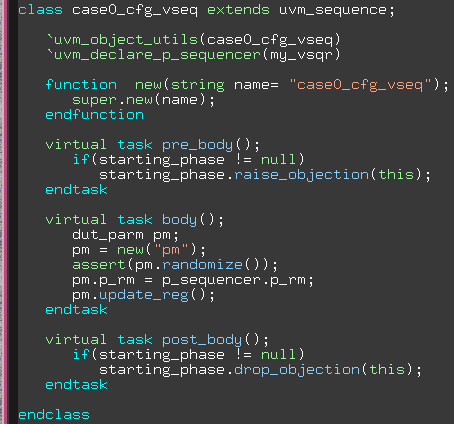

6.在virtual sequence 中,例化此类,随机,并调用update_reg:

这种约束形式在跨寄存器的约束多时特别有用。

你可能感兴趣的文章

小猪考试中~

查看>>

理解,promise~~

查看>>

微软之行

查看>>

Application OR Research

查看>>

唉,这个时候还算好吧

查看>>

有趣的考试~~

查看>>

试依然在考,烧依然在发~~

查看>>

OS我爱你~~

查看>>

2006年了

查看>>

今天好消息不少。。

查看>>

偶尔也会感慨。。

查看>>

难得的轻闲-_-

查看>>

明天开始复习咯!

查看>>

第二天

查看>>

郁闷的问题

查看>>

阶段性胜利。。

查看>>

有点儿累了,最近特别能吃

查看>>

project的架构模式

查看>>

总结一下细节问题

查看>>

重新整合了一下代码

查看>>